# plevin <u>SIGASPEC</u> SDEC ONS

| 2128022                  |

|--------------------------|

| Tue Jul 26 15:49:58 1988 |

|                          |

| Tue Jul 26 15:48:57 1988 |

| 74                       |

| Portrait                 |

| 600                      |

| 1100                     |

| After 60 lines           |

| 550                      |

| 750                      |

|                          |

# Table of Contents.

1

| 1 Introduction                                | . 1 |

|-----------------------------------------------|-----|

| 2 Terminology                                 |     |

| 3 Document Standards                          | . 4 |

| 3.1 Register Definition Syntax                |     |

| 3.2 Logical Operators                         | . 5 |

| 3.3 Timing Diagram Symbols                    | . 5 |

| 4 Functional Overview                         | . 6 |

| 4.1 Functional Unit Description               | . 7 |

| 4.1.1 Requestor                               | . 7 |

| 4.1.2 Server                                  | . 7 |

| 4.1.3 TCS Control Unit                        | . 8 |

| 4.1.4 Configuration/Status Unit               | . 8 |

| 4.2 System Operation                          | . 8 |

| 4.2.1 Function Requests                       | 8   |

| 4.2.2 Function Responses                      | 10  |

| 4.3 Basic Message Formats                     | 11  |

| 4.3.1 Read Messages                           | 11  |

| 4.3.1.1 Downstream                            | 11  |

| 4.3.1.2 Upstream                              | 12  |

| 4.3.2 Write Messages                          | 13  |

| 4.3.2.1 Downstream                            | 14  |

| 4.3.2.2 Upstream                              | 15  |

| 5 Detailed Functional Description             | 15  |

| 5.1 Requestor                                 | 16  |

| 5.1.1 Operation                               | 17  |

| 5.1.1.1 Overview                              | 17  |

| 5.1.1.2 RTC and related functions             | 19  |

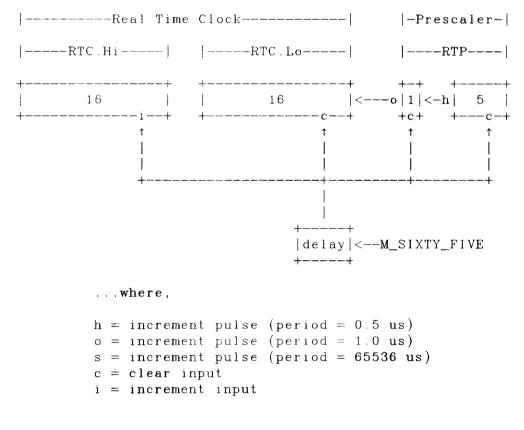

| 5.1.1.2.1 Real Time Clock and Prescaler       | 20  |

| 5.1.1.2.2 Time Of Next Interrupt              | 24  |

| 5.1.1.2.3 Priority Time Slot                  | 26  |

| 5.1.1.3 Function Request Types                | 28  |

| 5.1.1.4 T-Bus Request Screening               | 29  |

| 5.1.1.5 Initial Message Start/Retry Criterion | 30  |

| 5.1.1.5.1 Random Start/Retry                  | 30  |

| 5.1.1.5.2 Slotted Start/Retry                 |     |

| 5.1.1.5.3 Start/Retry Criterion Selection     | 35  |

| 5.1.1.6 Switch Tx Protocol Timers             | 38  |

| 5.1.1.6.1 Reject Timer                        |     |

| 5.1.1.6.2 Connection Timer                    |     |

| 5.1.1.6.3 Protocol Timer Programming          |     |

| 5.1.1.7 Anticipation Support                  |     |

| 5.1.1.7.1 Function Requests                   | 42  |

Preliminary Release Page 1

| 5.1.1.7.2  | Function Responses                | 44 |

|------------|-----------------------------------|----|

| 5.1.1.8    | Locked Sequences                  | 44 |

| 5.1.1.8.1  | Opening and Maintaining Locks     | 45 |

| 5.1.1.8.2  | Dropping Locks                    | 46 |

| 5.1.1.8.3  | Auto Drop                         | 47 |

| 5.1.1.9    | Stolen Bit Support                | 48 |

| 5.1.1.10   | Quick Drop                        | 49 |

| 5.1.1.11   | Reverse Profile Monitoring        | 49 |

| 5.1.1.12   | Error Detection and Reporting     | 51 |

| 5.1.1.12.1 | FQ Errors                         | 51 |

| 5.1.1.12.2 | Switch Errors                     | 53 |

| 5.1.1.12.3 | Remote Errors                     | 54 |

| 5.1.1.13   | Disabled Operation                | 55 |

| 5.1.1.14   | Configuration Registers           | 55 |

| 5.1.1.15   | Test Registers                    | 56 |

| 5.1.2      | Switch Message Protocol           | 62 |

| 5.1.2.1    | Physical Route Address Generation | 63 |

| 5.1.2.2    | Downstream Message Components     | 63 |

| 5.1.2.2.1  | Header                            | 64 |

| 5.1.2.2.2  | Body                              | 66 |

| 5.1.2.3    | Checksum Support                  | 66 |

| 5.1.2.4    | Checksum Calculation              | 68 |

| 5.1.2.4.1  | Header Partial Sum                | 68 |

| 5.1.2.4.2  | Message Checksum                  | 68 |

| 5.1.2.5    | T-Bus Interface                   | 69 |

| 5.1.2.6    | LCON Interface                    | 71 |

| 5.1.2.6.1  | Data Bus Enable Control           | 71 |

| 5.2 S      | erver                             | 73 |

| 5.2.1      | Operation                         | 74 |

| 5.2.1.1    | Overview                          | 74 |

| 5.2.1.2    | Anticipation Support              | 76 |

| 5.2.1.2.1  | Function Requests                 | 76 |

| 5.2.1.2.2  | Function Responses                | 77 |

| 5.2.1.3    | Locked Sequences                  | 78 |

| 5.2.1.4    | Stolen Bit Support                | 79 |

| 5.2.1.5    | Error Reporting                   | 80 |

| 5.2.1.6    | Disabled Operation                |    |

| 5.2.1.7    | Configuration Registers           | 81 |

| 5.2.1.8    | Test Registers                    | 84 |

| 5.2.2      | Switch Message Protocol           | 86 |

| 5.2.2.1    | Upstream Message Components       | 87 |

| 5.2.2.2    | Stolen and Error Messages         | 88 |

| 5.2.2.3    | Upstream Message Types            | 89 |

| 5.2.2.4    | Checksum Calculation              | 89 |

| 5.2.2.5    | Rejects                           | 91 |

Preliminary Release Page 2

| 5.2.3 T-Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 92  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2.4 LCON Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 92  |

| 5.2.4.1 Data Bus Enable Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 93  |

| 5.3 TCS Control Unit (TCU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 93  |

| 5.3.1 I/O Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 94  |

| 5.3.2 Read/Write Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 95  |

| 5.3.3 Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 97  |

| 5.3.4 Normal T-Bus Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 100 |

| 5.3.5 Special T-Bus Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 100 |

| 5.3.6 CSU Map Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 101 |

| 5.4 Configuration/Status Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 101 |

| 5.4.1 Normal Register Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 101 |

| 5.4.2 Synchronized Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 101 |

| 5.4.3 Interleaver Loader                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 102 |

| 5.4.3.1 Address Register Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 103 |

| 5.4.3.2 Data Register Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 104 |

| 5.4.4 Debug Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 105 |

| 5.4.5 Restriction Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 106 |

| 6 Programming Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 106 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 107 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 107 |

| , spectal representation of the second | 108 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 108 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 111 |

| o imposoription and imposor in the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 114 |

| 9 A.C./D.C. Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 120 |

. \

July 25, 1988

## 1 Introduction

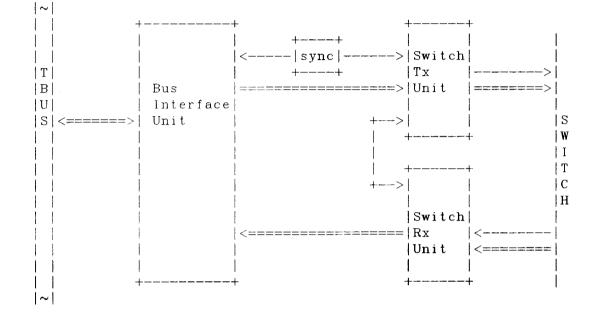

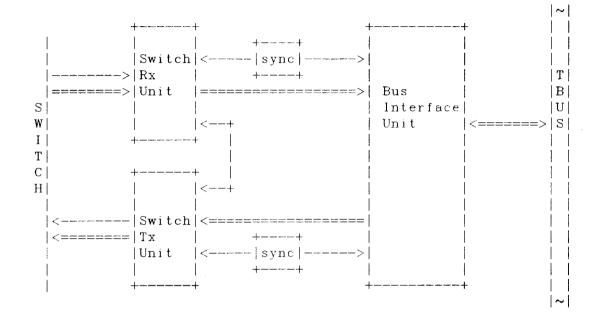

The SIGA is a gate array device which serves as the bidirectional interface between a Computational Node and the Switch network of the Butterfly II Parallel Processor. As such, the SIGA provides devices on each Computational Node with virtually transparent read and write data access to similar The devices on physically remote nodes. SIGA by accepting/presenting data via accomplishes this the standard interface that these devices support - namely the T-Bus - and then presenting/accepting this same data to the Butterfly Switch interface for transport.

This document will present both a detailed functional and operational description of the SIGA. It is intended to be used as a design guide for both hardware and software system engineers. This specification is necessarily limited ın its scope and thus will touch upon other Butterfly II-related subjects only when it is necessary for completeness. Therefore. it is assumed that the reader of this document has a general knowledge of the concepts of the Butterfly II architecture and operation. The reference documents are as follows:

T-Bus Specification (Ward Harriman)

Switch Gate Array Design Specification (Ward Harriman)

Butterfly II Level Converter Array Specification (Mike Sollins)

Switch Protocol Specification (Ward Harriman)

Reference Documents Figure 1

2 Terminology

The following terms will be used throughout this document:

Byte - Refers to an 8-bit quantity.

Preliminary Release

Page 1

BBN Advanced Computers Inc

Anticipation - A feature of the SIGA design that allows the SIGA to take advantage of certain parallel optimizations.

Downstream Node - The node which services a switch transaction.

Drop-Lock - When the Requestor negates Frame during a locked sequence, causing the Server to issue a FREE-LOCK.

Function Response - A generic term for the various incarnations of a response to a function request from some downstream T-Bus slave to an upstream This T-Bus slave. includes the transformations that the response undergoes as it travels from the downstream T-Bus, downstream SIGA, Switch, upstream SIGA, and finally the upstream T-Bus. (see Function Request)

Function Request - A generic term for the various incarnations of a request from some upstream T-Bus master to a downstream T-Bus slave. This includes the transformations that the request undergoes as it travels through the upstream T-Bus, upstream SIGA, Switch, downstream SIGA, and finally the downstream T-Bus. (see Function Response)

Final Locked message - The same as a Locked message except that the Switch path is released by letting Frame=0 for at least two Switch Intervals after the operation has been acknowledged.

Half-Word - Refers to a 16-bit quantity. (see Word)

Initial Locked message - Occurs under the same circumstances as the Unlocked message except that the Switch path is held open once the operation has been acknowledged without errors.

Local Errors - Errors which originate in the Requestor.

Logical Route Address - A 9-bit Switch node address generated from either the Interleaver or the T-Bus. This address is then transformed, possibly by randomizing some of the bits, into the Physical Route Address.

Locked message - A message which occurs when the Switch path was already locked and causes it continue to be locked after the operation has been acknowledged.

Message - With the exception of Reject, a Message is the

Preliminary Release Page 2

BBN Advanced Computers Inc

assertion of Frame (downstream message) or Reverse (upstream message) possibly with associated data on the data lines.

Message Acknowledgment - Also known as  $M_ACK$ . This refers to the assertion of Reverse for at least two Switch Intervals during a function response. It indicates that the downstream Server has Acknowledged the receipt of a Function Request.

Message Header - The part of a downstream Switch message that carries routing information. That part is stripped-off by the Switch and thus never reaches the downstream Server The message header for an upstream Switch message is null.

Message Body - The part of the downstream Switch message that carries the command, address, data, and checksum bytes.

Multi-Word Transfer - Refers to a read or write function request that involves more than one word (32 bit) of data.

Operational State - A SIGA initialization state which allows full operation of the SIGA.

Pad - A special class of downstream message which contains all zero's for data. It is used by the Requestor to hold the Switch path open while it awaits a message acknowledgement.

Physical Route Address - The transformation of the Logical Route Address after some of its bits have been randomized. The Physical Route Address is placed into the downstream Message Header.

Quick-Drop - This is an optimization in the Requestor where the  $R_FRAME$  signal is negated as soon as possible after an  $R_REVERSE$  is received.

Quiescent State - A SIGA initialization state which allows partial operation of the SIGA.

Remote Errors - Errors which originate in the Server.

Reject – An assertion of Reverse for one Switch Interval. Indicates that a message was rejected at either a Server or an SGA.

Sequence - A function request followed by a function response.

Preliminary Release

Page 3

BBN Advanced Computers Inc.

Split-Cycle - A T-Bus Read transaction where the Master releases the bus while the Slave is completing the transaction.

Switch Interval - The 25 ns period in which Switch data is propogated.

Switch Modulus - The number of ports that a basic switching element can handle. That number is currently eight.

Transaction - Another word for a Sequence.

Unlocked Message - Occurs when the Switch path had previously been "torn-down". This occurs whenever Frame was "O" for at least two Switch Intervals. Once the operation has been acknowledged, the path is torn-down again.

Upstream Node - The node which initiates a switch transaction.

Valid Message - A downstream message which carries a read or write request and does not violate switch protocol.

Word - Refers to a 32-bit quantity. (see Half-Word)

3 Document Standards

The following describes some of the standard syntax and expressions used in this document.

3.1 Register Definition Syntax

A typical register definition is shown in Figure 2. Referring to Figure 2, the "-" in any bit indicates that this bit is a "don't care" on a write and indeterminate on a read. If "-" totally fills a field of eight bits, that field should NEVER be written to but of course, can be read from. The entire register may be referred to in any one of the following ways: The sub-fields, shown in Figure 2 within "[]", can be referred to in various ways. For instance, the "Cnt" subfield could be referred to as:

Page 4

Register: Protocol\_Timer\_Config<15..0>

| 15    |       | 0      |

|-------|-------|--------|

|       |       |        |

| 30    | 30    | 70     |

| CCCC  | PPPP  | NNNNNN |

| [Cnt] | [Pre] | [Con]  |

Register Syntax Definition Figure 2

- (1) Protocol\_Timer\_Config<15..0>

- (2) Protocol\_Timer\_Config

- (3) PTC < 15...0 >, or

(4) PTC

- (1) Protocol\_Timer\_Config<15..12>

- (2) Protocol\_Timer\_Config.Cnt<3..0>

- (3) Protocol\_Timer\_Config.Cnt

- (4) PTC.Con

3.2 Logical Operators

Figure 3 shows the standard operators used in this document.

3.3 Timing Diagram Symbols

Timing diagrams use ASCII characters to represent signal states. Figure 4 illustrates some of those symbols and their associated meanings. In addition, if no clock signal is present in a timing

Preliminary Release

Page 5

| FUNCTION        |

|-----------------|

|                 |

| logical "and"   |

| logical "or"    |

| logical "exor"  |

| logical "not"   |

| logical "exnor" |

| concatenate     |

|                 |

# Example - Logical Operators Figure 3

| SYMBOL | MEANING           |             |

|--------|-------------------|-------------|

| ====== | ======            |             |

| Н      | logical "1"       |             |

| _      | logical "O"       |             |

|        | continue previous | state       |

| ?????  | state unknown and | unimportant |

# Example - Logical Operators Figure 4

diagram, it is assumed that each character column represents an active transition of the appropriate clock.

4 Functional Overview

The following describes the basic functionality of the SIGA at a conceptual level.

Preliminary Release Page 6

## 4.1 Functional Unit Description

The SIGA is composed of four basic elements, the Requestor, Server, Control Net Interface and the Config/Status Unit. Although these are physically co-located and share some common logic and control, they are functionally independent units and will be described separately.

## 4.1.1 Requestor

The Requestor is a T-Bus slave device which transparently couples physically remote T-Bus slave devices to the local T-Bus by interacting with both the Switch and the downstream Server. The Requestor appears to the current T-Bus master as a segment of memory which is out of the range of physical memory at the local node. Signals on the T-Bus alert the Requestor that the current access is for a remote location and the Requestor then initiates the switch transaction to comply with the master's read or write request.

Since the transaction is not completed immediately (indicated by the Requestor with a PROMISE response), the requesting T-Bus master follows the T-Bus protocol and releases the bus so that other devices may use it. The Requestor eventually regains control of the T-Bus, alerts the requesting master that the read or write operation has been completed, and returns data or an error indication. If the current sequence is locked, as requested by the T-Bus master, and no errors are encountered, the Requestor holds open the Switch path for the next transaction rather than rearbitrating for a new Switch path. Any errors that may have occured during this operation are signalled to the T-Bus Master through the ERROR response.

#### 4.1.2 Server

The Server acts as a master on the local T-Bus of the downstream node and services requests from the upstream node's Requestor. When a new valid message enters the Server from the Switch, the Server obtains the local T-Bus; locks the T-Bus slave, if desired; performs the read or write operation; and then returns the data and/or error byte to the Upstream Node's Requestor. The Server can also initiate other special operations independently

Preliminary Release

of receiving a new Switch message. This operation, known as drop-locks, is described elsewhere in this document.

## 4.1.3 TCS Control Unit

The basic purpose of the TCS Control Unit (TCU) is to give the serial interface of the TCS Control Slave Processor access to the T-Bus interface - in essence, to act as a protocol converter. A secondary function is to allow the TCS Slave Processor DIRECT access to some of the internal functions of the SIGA, rather than forcing it to access via the T-Bus interface. This is useful for fault-tolerance and "out-ofband" functions such as bootstrapping.

#### 4.1.4 Configuration/Status Unit

The Config/Status Unit (CSU), acting as a T-Bus slave, allows read/write access to all programmable parameters of the Requestor, Server and TCS Control Unit. The CSU also provides convenient access to the internal state of certain nodes for testability.

#### 4.2 System Operation

From a high-level view, the SIGA is one link in the chain of devices that allows a T-Bus device to fulfill a function request with a function response. The role of the SIGA in fulfilling both function requests and responses is now described.

#### 4.2.1 Function Requests

A local T-Bus master in the upstream node, usually the CPU, initiates the sequence by placing an address on the T-Bus, which is detected by the SIGA Requestor as a remote access request. During the T-Bus request phase, the SIGA stores the address, produces and stores the bid, and command bytes. It then initiates the downstream message at the Switch interface by asserting Frame and placing the bid symbols on the Switch data lines. Normally, this message tramsmission is initiated by the SIGA immediately upon receiving the address from the T-Bus,

Preliminary Release

Page 8

but it can be programmed to start later. On a write, the SIGA loads its data registers during the response phase of the T-Bus cycle. All operations are split-cycle and thus the Server will release the bus while it processes the transaction request.

If there is no Switch contention, the assembled message continues to be transmitted and is ultimately appended with a checksum derived from the message data bytes. If there is a Reject is generated by the Switch and Switch contention, eventually makes its way upstream to the Requestor via the Reverse line When this happens, the Requestor negates Frame, waits for a predetermined amount of time and then retries the message by asserting Frame and sending the message components stored from the first attempt.

Sometime after the beginning of the message reaches the Server at the downstream node (i.e. it is not Rejected by the Switch), that Server begins arbitration for its local bus to complete the transaction. If the device on the downstream node is locked to a remote bus master other than the Server. the Server issues a Reject which propogates upstream and i s eventually detected at the upstream Requestor. This Reject i s treated exactly the same by the Requestor as a Reject from theSwitch. Note that this is the ONLY instance in which the Server will issue a Switch Reject - an Initial Message.

Assuming that the Requestor receives neither a Switch Reject a Server Reject, it deasserts Frame for one switch interval nor while it sends the checksum byte. Within the checksum byte, the "forward" bit is reset. This event would normally cause the forward drivers of the SGA's to turn off after they send the checksum byte. However, the current implementation of the SGA ignores this bit and turns-on its foward drivers in response to the Frame profile. The Requestor then sends the Pad message (all 0's) and awaits a response from the Server. Note that the forward bit is not used by the current SGA's.

In the meanwhile, the downstream Server begins processing the request by arbitrating for the local T-Bus. Assuming that the target downstream bus slave was not locked to а downstream the Server, the Server obtains the local master other than bus and possibly opens the local memory lock. The Server will the lock only if this action was requested in the open downstream message. This would occur if the master the on

Preliminary Release Page 9

upstream node's local bus requested an OPEN lock when it initiated a transaction through it's associated Requestor.

Once the downstream Server obtains the local bus, it makes a function request to perform the appropriate read or write operation. The only exception to this is when the Server detects a checksum error in the downstream message. If this occurs, instead of making a request, the Server releases control of the T-Bus, creating a "dead" bus cycle and thereby aborting the transaction. This action on an aborted transaction should eliminate any unwanted side-effects if the switch message is corrupted.

## 4.2.2 Function Responses

Assuming that a read transaction was requested, the downstream Server completes the read as a normal local T-Bus master. As soon as the read data is obtained by the Server, a message is returned to the upstream Requestor. This happens (over the same data wires which the downstream message was sent) by asserting Reverse and applying data to the Switch data lines. The upstream message contains the read data, and possible error data; a checksum; and а message acknowledgement, or M\_ACK which is implicit in the assertion of Reverse for at least two Switch intervals. If a write transaction was requested, the Server writes the data to the address specified in the downstream message and sends an M ACK with an error byte data and checksum after the back data has been accepted by the slave on the local T-Bus. In short, a read returns data/errors and an acknowledgement whereas a write only returns possible errors and an acknowledgement.

In the case of a read transaction, the upstream Requestor detects the M\_ACK and alerts the local split-cycle master which initiated the request that the requested data has been returned. That master then completes the operation by retrieving the data. In the case of a write transaction, the Requestor also alerts the initiating local bus master that the write was completed but returns only error information.

In the absence of errors, the Requestor will continue to hold the Switch path open by asserting Frame only if the sequence was initiated with an OPEN. If that master decides to release the

Preliminary Release

Page 10

lock, the Requestor will tear-down the switch connection by negating Frame and will enter its unlocked idle state. This is the state that it was in at the beginning of this discussion of function requests. If the upstream bus master does not release the lock, it may initiate another read or write transaction. This and subsequent transactions are referred to as locked transactions. Outside of errors, locked transactions end only when the upstream T-Bus master which OPENed. MAINTAINEd or BYPASSed the SIGA Requestor lock decides to release that lock with a FREE-LOCKS command.

Subsequent message transactions in a locked sequence differ from the initial transactions described above in three major ways. First. locked messages do not contain any bids because the path has already been established. Second, the Switch will never issue a Reject because the path has already been established and is being reserved for the Requestor. And third, the downstream Server will never issue a Reject because it will already have exclusive use of the local memory lock. Aside from these exceptions, subsequent locked transactions occur in exactly the same manner as unlocked transactions. As mentioned previously, the upstream T-Bus the SIGA Requestor MUST release that lock master owning explicitly with a FREE-LOCKS.

#### 4.3 Basic Message Formats

Message formats differ mainly with the type of function request; read or write. Within a read or write message, the downstream and upstream messages corresponding to a function request and response also differ.

## 4.3.1 Read Messages

Read message formats differ mainly depending on whether or not they are downstream or upstream messages.

## 4.3.1.1 Downstream

Downstream Read messages are differentiated partly because of their data format and partly because of the state of Frame at the

Preliminary Release

BBN Advanced Computers Inc.

beginning and end of the message. The formats for three possible SIGA Requestor read operations are considered:

- An Unlocked Read occurs when the Switch path had previously been "torn-down". This occurs whenever Frame was "O" for at least two Switch Intervals. Once the operation has been acknowledged, the path is torn-down again.

- 2) An Initial Locked Read occurs under the same circumstances as the Unlocked Read except that the Switch path is held open once the operation has been acknowledged.

- 3) A Locked Read is a read which occurs when the Switch path was already locked and it continues to be locked after the operation has been acknowledged.

In all cases, the Requestor waits for a Message Acknowledgement  $(M\_ACK)$  from the downstream Server before completing the message. Figure 5 illustrates the three read message types for a two column switch. In this figure, the "d" field indicates the direction of the LCON drivers which interface data with the LCON. When d = "P" (Output), the Requestor is sourcing data to the Requestor/LCON interface. When d = "I" (Input), the LCON drivers are sourcing data to the Requestor/LCON interface. The "f" field is the state of the Frame bit. Data is MSB at the left of the field.

### 4.3.1.2 Upstream

When a downstream read message has been received and processed by a Server, an upstream message is returned to the initiating Requestor based on the operation requested. Under normal conditions, the Upstream Message is composed of two parts: the returned data (with checksum) and the M\_ACK (Message Acknowledge). The returned data is the contents of the remote memory location read, which can be 1, 2 or 4 words in length. With the exception of rare error conditions, the actual message data field is almost always a multiple of four.

Preliminary Release

Page 12

I.

| Unlocked<br>Read<br>=======                                                                                                                            | Initial<br>Locked Read<br>=======                                                                                                                      | Locked<br>Read<br>=======                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| d f data                                                                                                                                               | df data                                                                                                                                                | df data                                                                                                                                                    |

| P 0 xxxxxxx<br>P 0 xxxxxxx<br>P 1 -bid1<br>P 1 -bid2<br>P 1 -cmd<br>P 1 -addr1<br>P 1 -addr2<br>P 1 -addr3<br>P 0 -check<br>I 1 xxxxxxx<br>I 1 xxxxxxx | P 0 xxxxxxx<br>P 0 xxxxxxx<br>P 1 -bid1<br>P 1 -bid2<br>P 1 -cmd<br>P 1 -addr1<br>P 1 -addr2<br>P 1 -addr3<br>P 0 -check<br>I 1 xxxxxxx<br>I 1 xxxxxxx | P 1 XXXXXXX<br>P 0 XXXXXXX<br>P 1 -cmd<br>P 1 -addr1<br>P 1 -addr2<br>P 1 -addr3<br>P 0 -check<br>I 1 0000000<br>I 1 0000000<br>I 1 0000000<br>''<br>M_ACK |

| "<br>M_ACK<br>and read data<br>"<br>I O xxxxxxx<br>P O xxxxxxx                                                                                         | "<br>M_ACK<br>and read data<br>"<br>I 1 xxxxxxx<br>P 1 xxxxxxxx                                                                                        | and read data<br>"<br>I 1 xxxxxxxx<br>P 1 xxxxxxxx                                                                                                         |

# Read Switch Message Format - Downstream Figure 5

Figure 6 illustrates the upstream message. The "r" field is the Reverse signal. Data is MSB at left of the field.

# 4.3.2 Write Messages

Write message formats differ mainly depending on whether or not they are downstream or upstream messages.

١

1 -check--0 xxxxxxxx

Read Switch Message Format - Upstream Figure 6

#### 4.3.2.1 Downstream

Downstream Write messages are differentiated partly because of their data format and partly because of the state of Frame at the beginning and end of the message. The formats for three possible SIGA Requestor write operations are considered: In all cases, the Requestor waits for a Message Acknowledgement (M\_ACK) from the downstream Server before completing the message. Figure 7 illustrates the three write message types for a two column switch. In the figure, The "d" field is the direction of the LCON drivers which interface data with the SGA. When d = I, the Requestor is sourcing data to the Requestor/LCON interface. When d = P, the LCON drivers are sourcing data to the Requestor/LCON interface. The "f" field is the state of the Frame bit. Data is MSB at left of the field.

- An Unlocked Write occurs when the Switch path had previously been "torn-down" by the fact that Frame was "0" for at least two Switch Intervals. Once the operation has been acknowledged, the path is torndown again.

- 2) An Initial Locked Write occurs under the same circumstances as the Unlocked Write except that the Switch path is held open once the operation has been acknowledged.

- 3) A Locked Write is a write which occurs when the Switch path was already locked and it continues to be locked after the operation has been acknowledged.

#### 4.3.2.2 Upstream

When a downstream write message has been received and processed by a Server, an upstream message is returned to the initiating Requestor based on the operation requested. Under some conditions, the Server will not act on the downstream message and will instead send a Reject back to the Requestor. Under normal conditions however, upstream messages contain an M\_ACK, an error byte (normally all 0's) and a checksum.

The following illustrates the only possible return message for a write. The "r" field is the Reverse signal. Data is MSB at left of field.

# 5 Detailed Functional Description

The Requestor, Server, TCU and Configuration/Status Unit are now described in detail.

X

| Unlocked<br>Write<br>====== | Initial<br>Locked.Write<br>======= | Locked<br>Write<br>======= |